Chip Structure

- Base Layer : P-TEOS*

- Metal Layer : TiN / AI-0.5%Cu

- Passivation Layer : HDP* / P-SiN (option) NSG* / Polyimide

*TEOS : Tetraethoxysilane

*HDP : High Density Plasma

*NSG : Non-doped Silicate Glass

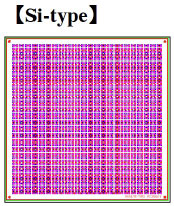

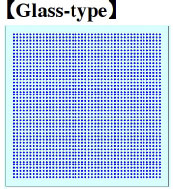

| Specifications | Si | Glass | |

| TYPE | A | B | B** |

| Wafer Size | 8 inch | 8 inch | 8 inch |

| Wafer Thickness | 725±25μm | 725±25μm | 700±70μm |

| Chip Size | 10.0mm ♦ | 10.0mm ♦ | 10.0mm ♦ |

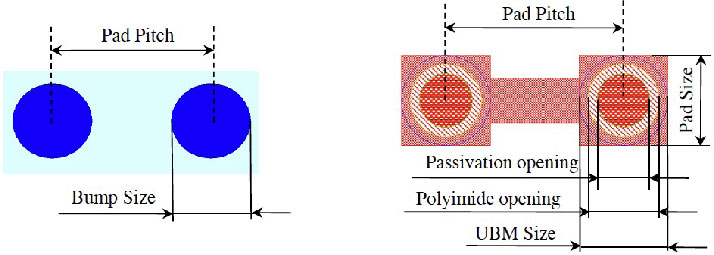

| Bump pitch | 200μm | 200μm | 200μm |

| Function | Daisy Chain | Daisy Chain | x |

| Pad config | Area | Area | Area |

| Electrode | Ball Mounted Solder Bump | Cu Pillar | Cu Pillar |

| Pad Size | 100μm ♦ | 100μm ♦ | x |

| Passivation opening | φ60μm • | φ60μm • | x |

| Polyimide opening | φ80μm • | φ80μm • | x |

| UBM Size | φ100μm • | φ90μm • | φ90μm • |

| Bump Size | φ100μm • | φ90μm • | φ90μm • |

| Scribe width | 100μm | 100μm | x |

| Number of Pad | 2116 pads/chip (46×46) | 2116 pads/chip (46×46) | x |

| Number of Chip | 228 chips/wafer | 228 chips/wafer | 228 chips/wafer |

| • Top Side ♦ Bottom Side |

**Glass die do not have daisy-chain function and no alignment marks or patterns on die